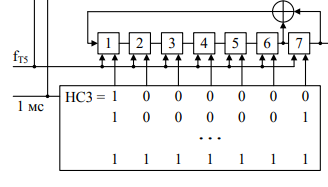

Необходимо написать код на ПЛИС c использованием языка Verilog. Необходимо сделать 7 регистров, в которые загружаются биты данных 1 0 0 0 0 0 0. После загрузки данных (в регистр номер 1 - загружается единица, в регистр 2 - 0 и т.д), регистры сдвигаются от первого ко второму, от второго к третьему, от третьего к четвертому … С регистра 6 выходит сигнал, которые суммируется с регистром 7 по модулю 2 и подается на первый регистр. Выходным является сигнал с регистра 7. Все бы ничего, но вот частота сдвига регистров и частота загрузки состояний этих регистров разные, а именно частота загрузки равна 1 кГц, а частота сдвига 10.230 МГц. Эти частоты сделать не проблема. Проблема в том, что при компиляции программа вылезает ошибка Error (10028): Can’t resolve multiple constant drivers for net … ( на фото Ft5 - 10.230 МГц)

Вот часть кода, в котором возникает ошибка ( kh_clk - частота 1 кГц, clk - частота 10.230 МГц)

wire [6:0] ca1;

assign ca1 = {q1,q2,q3,q4,q5,q6,q7};

always@( posedge kh_clk)

begin

if(reset)

begin

q1 <= 1'b0;

q2 <= 1'b0;

q3 <= 1'b0;

q4 <= 1'b0;

q5 <= 1'b0;

q6 <= 1'b0;

q7 <= 1'b0;

end

end

always@(posedge clk)

begin

if (!reset)

begin

q1 <= next_q1;

q2 <= q1;

q3 <= q2;

q4 <= q3;

q5 <= q4;

q6 <= q5;

q7 <= q6;

end

end

always@(posedge clk)

begin

next_q1 = q6 ^ q7;

end